全国产技术下大陆芯片制造瓶颈:专家称仅能实现28nm工艺

台湾芯片专家指出,若采用纯国产供应链制造芯片,中国大陆企业仅能实现28nm工艺量产。引入国外技术设备可突破至7nm节点,预计2030年前完成14nm及7nm国产化。设备壁垒主要体现在EUV光刻机领域,国产DUV光刻机技术已接近成熟,但需配合刻蚀设备实现先进制程突破。

全国产技术下大陆芯片制造瓶颈:专家称仅能实现28nm工艺

前沿导读

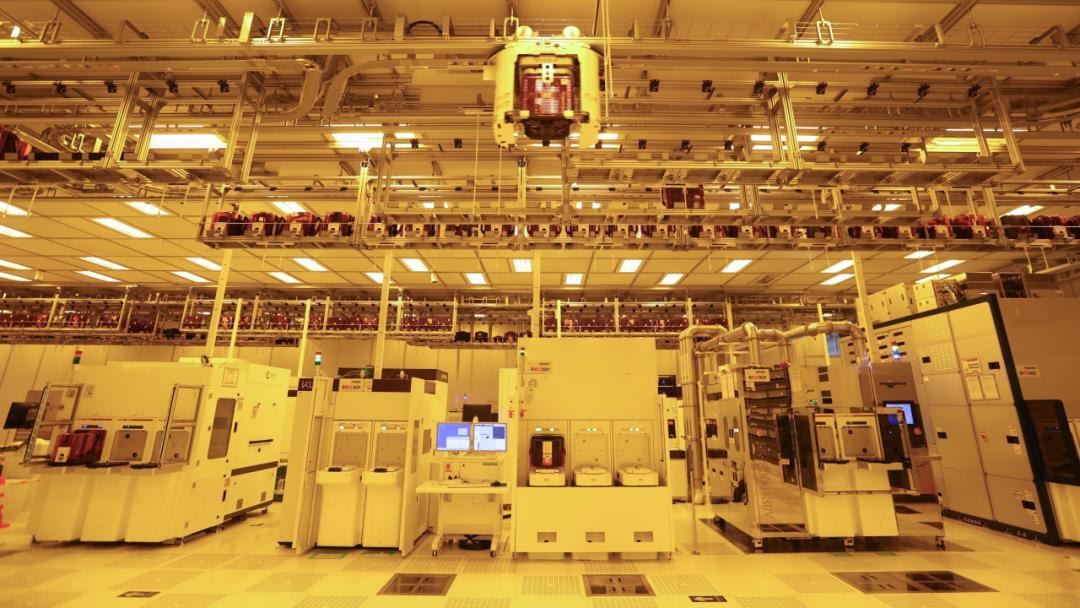

在乌凌翔主持的《论政天下》节目中,中国台湾青辉半导体总经理叶国光指出,纯国产供应链下大陆芯片量产水平仅能达到28nm节点。若引入国外技术设备辅助,可实现N+2工艺的7nm节点或N+3工艺的7nm+节点。

2030年前预计实现14nm、7nm(N+1)工艺国产化。当前芯片工艺以台积电技术为标准,其5nm节点晶体管密度达170-177 MTr/mm²,而国产N+3工艺密度为113-125 MTr/mm²,虽优于7nm但不及5nm水平。

设备壁垒

台积电5nm N5工艺晶体管密度达170-177 MTr/mm²,国产N+3工艺密度为113-125 MTr/mm²。核心差距在于制造设备,台积电已全面采用EUV技术,而大陆企业仍依赖浸润式DUV光刻机加自对准四重图案化技术。

芯片尺寸扩大反映技术瓶颈,微电子产业需在最小尺寸实现高性能低功耗。多重曝光工艺存在晶圆层对准精度问题,自对准多重图案化需沉积刻蚀设备辅助。

当前国产先进芯片依赖ASML DUV光刻机,多重曝光需两次光刻-刻蚀交替。自对准技术只需一次曝光,但需沉积刻蚀设备配合。

28nm工艺通过自对准多重图案化可实现14nm,再经沉积刻蚀可达到7nm节点。DUV技术需多次曝光,成本高于EUV技术。

中微半导体等企业已开发5nm刻蚀设备,但国产光刻机产能和良品率仍待提升。2024年国产干式DUV光刻机硬件指标已超日本佳能。

国产供应链

平面晶体管技术(22nm以下)已实现国产替代,Fin FET技术(14nm-3nm)部分环节自主可控。中芯上海/南方已建立Fin FET生产线,但设备仍依赖海外供应商。

EUV光刻机领域完全依赖ASML,国产原型机尚未量产。GAA结构应用在2nm以下工艺,因无法获取EUV光刻机,中国在该领域进展缓慢。

解决14nm工艺自主可控是关键,国产干式DUV光刻机已接近浸润式技术。配合中微半导体等设备,逐步突破7nm节点。

本文链接:/article/全国产技术下大陆芯片制造瓶颈专家称仅能实现28nm工艺

转载请注明出处,谢谢!